上拉电阻定义

上拉电阻是电阻,用于确保在没有输入信号的情况下将导线拉至高逻辑电平。

什么是下拉电阻?

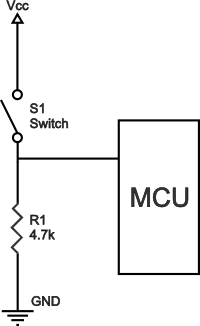

下拉电阻的工作方式与上拉电阻相同,只是它们将引脚拉至逻辑低电平值。它们连接在地和设备上的相应引脚之间。在图中可以看到数字电路中的下拉电阻的示例。按钮开关连接在电源电压和微控制器引脚之间。在这样的电路中,当开关关闭时,所述微控制器的输入是在逻辑高值,而当开关断开时,下拉电阻器向下拉动输入电压到地(逻辑0值),则防止输入处的未定义状态。下拉电阻必须具有比逻辑电路阻抗更大的电阻,

下拉电阻

上拉电阻值

上拉电阻的适当值受两个因素的限制。第一个因素是功耗。如果电阻值太低,则高电流将流过上拉电阻,加热器件并在开关闭合时耗尽不必要的电量。这种情况称为强上拉,当需要低功耗时可以避免这种情况。第二个因素是开关打开时的引脚电压。如果上拉电阻值太高,结合输入引脚的大漏电流,则当开关打开时输入电压可能变得不足。这种情况称为弱上拉。上拉电阻的实际值取决于输入引脚的阻抗,这与引脚的漏电流密切相

根据经验,使用的电阻至少比输入引脚阻抗值小10倍。在工作电压为5V的双极逻辑系列中,典型的上拉电阻值为1-5kΩ。对于开关和电阻传感器应用,典型的上拉电阻值为1-10kΩ。如果有疑问,使用开关时的良好起点是4.7kΩ。某些数字电路(如CMOS系列)具有较小的输入漏电流,允许更高的电阻值,从大约10kΩ到1MΩ。使用较大电阻值时的缺点是输入引脚对电压的响应变化较慢。这是上拉电阻和形成RC电路的导线的线电容之间的耦合的结果。R和C的产物越大,电容充电和放电所需的时间越长,因此电路越慢。在高速电路中,大的上拉电阻有时会限制引脚可靠地改变状态的速度。

上拉和下拉电阻的典型应用

当开关或其他输入与微控制器或其他数字门接口时,通常使用上拉和下拉电阻。大多数微控制器都内置可编程上拉/下拉电阻,因此需要的外部元件更少。可以直接将开关与这种微控制器连接。上拉电阻通常比下拉电阻更常用,尽管有些微控制器系列同时具有上拉和下拉电阻。

它们通常用于模数转换器,以提供受控电流流入电阻传感器。

另一个应用是I2C协议总线,其中使用上拉电阻使单个引脚用作输入或输出。未连接到总线时,引脚悬空在高阻态。

下拉电阻也用于输出,以提供已知的输出阻抗。